1. Tujuan

a. Mengetahui apa saja guidelines to handling and using cmos devices

b. Mengetahui bentuk rangkaian guidelines to handling and using cmos devices

Alat:

1. Power supply

2. Ground

Berfungsi sebagai penghantar arus listrik langsung ke bumi atau tanah

1.

Gerbang Logika (Logic Gates) adalah sebuah entitas untuk melakukan pengolahan input-input yang berupa bilangan biner (hanya terdapat 2 kode bilangan biner yaitu, angka 1 dan 0) dengan menggunakan Teori Matematika Boolean sehingga dihasilkan sebuah sinyal output yang dapat digunakan untuk proses berikutnya.

2. Materi

Pedoman berikut harus dipatuhi saat menggunakan perangkat keluarga CMOS:

1. Penanganan IC CMOS yang tepat sebelum digunakan dan juga setelah dipasang di papan PC sangat penting karena IC ini sangat rentan terhadap kerusakan oleh pelepasan elektrostatik. Meskipun semua IC CMOS memiliki jaringan perlindungan bawaan untuk menjaga mereka dari pelepasan elektrostatik, tindakan pencegahan harus diambil untuk menghindari kemungkinan seperti itu. Saat menangani chip yang tidak dilepas, potensial perbedaan harus dihindari. Ini adalah praktik yang baik untuk menutupi chip dengan foil konduktif. Setelah chip telah dipasang di papan PC, adalah praktik yang baik lagi untuk menempatkan klip konduktif atau pita konduktif pada terminal papan PC. Ingat bahwa papan PC tidak lain adalah ekstensi prospek IC yang dipasang di atasnya kecuali diintegrasikan dengan sistem keseluruhan dan tegangan hadir.

2. Semua input yang tidak digunakan harus selalu terhubung ke VSS atau VDD tergantung pada logika yang terlibat. Input mengambang dapat mengakibatkan operasi logika yang rusak. Dalam kasus jenis perangkat arus tinggi seperti buffer, itu juga dapat menyebabkan hilangnya daya maksimum chip yang terlampaui, sehingga menyebabkan kerusakan perangkat. Resistor (biasanya 220 k hingga 1 M sebaiknya terhubung antara input dan VSS atau VDD jika ada kemungkinan terminal perangkat menjadi sementara tidak terhubung atau terbuka.

3. Kisaran tegangan pasokan operasi yang direkomendasikan adalah 3–12 V untuk seri A (3–15 V menjadi peringkat maksimum) dan 3–15 V untuk seri B dan seri UB (3–18 V menjadi maksimum). Untuk CMOS Sirkuit aplikasi IC yang dioperasikan dalam mode linear di atas sebagian rentang tegangan, seperti sebagai osilator RC atau kristal, VDD minimum 4 V direkomendasikan.

4. Sinyal input harus dipertahankan dalam kisaran tegangan catu daya VSS < Vi < VDD (−0,5 V < Vi < VDD + 0,5 V menjadi maksimum mutlak). Jika sinyal input melebihi rentang sinyal input yang direkomendasikan, arus input harus dibatasi hingga ± 100 mA.

5. IC CMOS seperti IC TTL pull-up aktif tidak dapat dihubungkan dalam konfigurasi WIRE-OR. Penjajaran input dan output gerbang juga direkomendasikan untuk IC dalam paket yang sama saja.

6. Sebagian besar perangkat clocked CMOS memiliki peringkat waktu naik dan turun maksimum biasanya 5–15 s. Perangkat mungkin tidak berfungsi dengan baik dengan waktu naik dan turun yang lebih besar. Pembatasan, bagaimanapun, tidak berlaku untuk IC CMOS yang telah membangun Schmitt pemicu pembentukan di sirkuit jam.

a. Buka aplikasi proteus

b. Pilih komponen yang dibutuhkan, pada rangkaian ini dibutukan komponen resistor, logic state, gerbang NOT, transistor serta led dan ground

c. Rangkai setiap komponen menjadi rangkaian yang diinginkan

d. Ubah spesifikasi komponen sesuai kebutuhan

e. Jalankan simulasi rangkaian.

5. Gambar rangkaian

Pada rangkaian ini menggunaka pmos dan n mosfet, ketika input berlogika 0 maka arus akan mengalir dari power menuju q1 lalu masuk ke drain nmosfet lalu menuju ground sehingga output akan berlogika satu . Begitu pula jika inputnya 1.

Ketika input dalam status TINGGI (logika '1'), P-channel MOSFET Q1 berada di keadaan cut-off sementara N-channel MOSFET Q2 sedang melakukan. MoSFET yang melakukan jalur dari tanah ke output dan outputnya RENDAH (logika '0'). Ketika input dalam status RENDAH (logika '0'), Q1 dalam konduksi sementara Q2 dipotong. Perangkat P-channel yang melakukan menyediakan jalur agar VDD muncul pada output, sehingga output dalam status TINGGI atau logika '1'. Masukan mengambang bias menyebabkan konduksi MOSFETs dan kondisi arus pendek. Karena itu harus dihindari. Itu juga terbukti dari Gbr. 5.34 bahwa tidak ada jalur konduksi antara VDD dan tanah di salah satu kondisi input, yaitu ketika input berada dalam logika '1' dan '0' menyatakan. Itulah sebabnya praktis ada hilangnya daya nol dalam kondisi statis. Hanya ada disipasi daya dinamis, yang terjadi selama beralih operasi karena kapasitas gerbang MOSFET dibebankan dan dipulangkan. Kekuatan menghilang berbanding lurus dengan frekuensi pengalihan.

6. Video

7. Contoh soal

1. Apa perbedaan antara NMOS dan PMOS?

Jawab: NMOS dibangun dengan sumber dan saluran tipe-n dan substrat tipe-p, sedangkan PMOS dibangun dengan sumber dan saluran tipe-p dan substrat tipe-n. Dalam NMOS, pembawa adalah elektron, sedangkan di PMOS, pembawa adalah lubang. Ketika tegangan tinggi diterapkan ke gerbang, NMOS akan berjalan, sedangkan PMOS tidak. Selanjutnya, ketika tegangan rendah diterapkan di gerbang, NMOS tidak akan berjalan dan PMOS akan berjalan. NMOS dianggap lebih cepat daripada PMOS, karena pembawa di NMOS, yang merupakan elektron, bergerak dua kali lebih cepat dari lubang, yang merupakan pembawa di PMOS. Tetapi perangkat PMOS lebih kebal terhadap derau daripada perangkat NMOS. Lebih lanjut, IC NMOS akan lebih kecil dari IC PMOS (yang memberikan fungsionalitas yang sama), karena NMOS dapat memberikan setengah dari impedansi yang disediakan oleh PMOS (yang memiliki geometri dan kondisi operasi yang sama).

2. Apa perbedaan antara CMOS dan TTL?

Jawab: • Komponen TTL relatif lebih murah daripada komponen CMOS yang setara. Namun, teknologi CMO cenderung ekonomis dalam skala yang lebih besar karena komponen rangkaian lebih kecil dan memerlukan pengaturan yang lebih sedikit dibandingkan dengan komponen TTL.

• Komponen CMOS tidak mengkonsumsi daya selama keadaan statis, tetapi konsumsi daya meningkat seiring dengan clock rate. TTL, di sisi lain, memiliki tingkat konsumsi daya yang konstan.

• Karena CMOS memiliki persyaratan arus yang rendah, konsumsi daya menjadi terbatas dan sirkuit, oleh karena itu, lebih murah dan lebih mudah dirancang untuk manajemen daya.

• Karena waktu naik dan turun yang lebih lama, sinyal digital di lingkungan CMO menjadi lebih murah dan rumit.

• Komponen CMOS lebih sensitif terhadap gangguan elektromagnetik daripada komponen TTL.

8. Problem

1. Apa yang harus diperhatika terkait semua input dalam menggunakan perangkat keluarga CMOS?

Jawab: Semua input yang tidak digunakan harus selalu terhubung ke VSS atau VDD tergantung pada logika yang terlibat. Input mengambang dapat mengakibatkan operasi logika yang rusak. Dalam kasus jenis perangkat arus tinggi seperti buffer, itu juga dapat menyebabkan hilangnya daya maksimum chip yang terlampaui, sehingga menyebabkan kerusakan perangkat. Resistor (biasanya 220 k hingga 1 M sebaiknya terhubung antara input dan VSS atau VDD jika ada kemungkinan terminal perangkat menjadi sementara tidak terhubung atau terbuka.

2. Berikan contoh rangkaian inverter CMOS!

Jawab:

9. Soal pilihan ganda

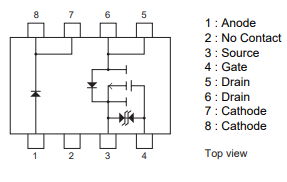

1. Gambar dibawah ini disebut?

a. NMosfet

b. transistor

c. NPN

d. Pmosfet

Jawab: d

2. Manakah pernyataan dibawah ini yang salah?

a. IC CMOS seperti IC TTL pull-up aktif tidak dapat dihubungkan dalam konfigurasi WIRE-OR

b. Jika sinyal input melebihi rentang sinyal input yang direkomendasikan, arus input harus dibatasi hingga ± 100 mA.

c. Sebagian besar perangkat clocked CMOS memiliki peringkat waktu naik dan turun maksimum biasanya 5–15 s.

d. Input mengambang tidak dapat mengakibatkan operasi logika yang rusak

Jawab: d

10. Download file

HTML: disini

File rangkaian: disini

Video:

Datasheet mosfet: disini

Tidak ada komentar:

Posting Komentar